光刻工藝革新 LELE、SADP與EUV技術大比拼

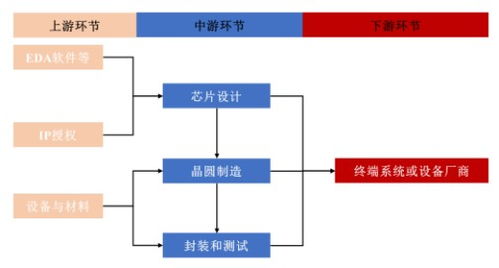

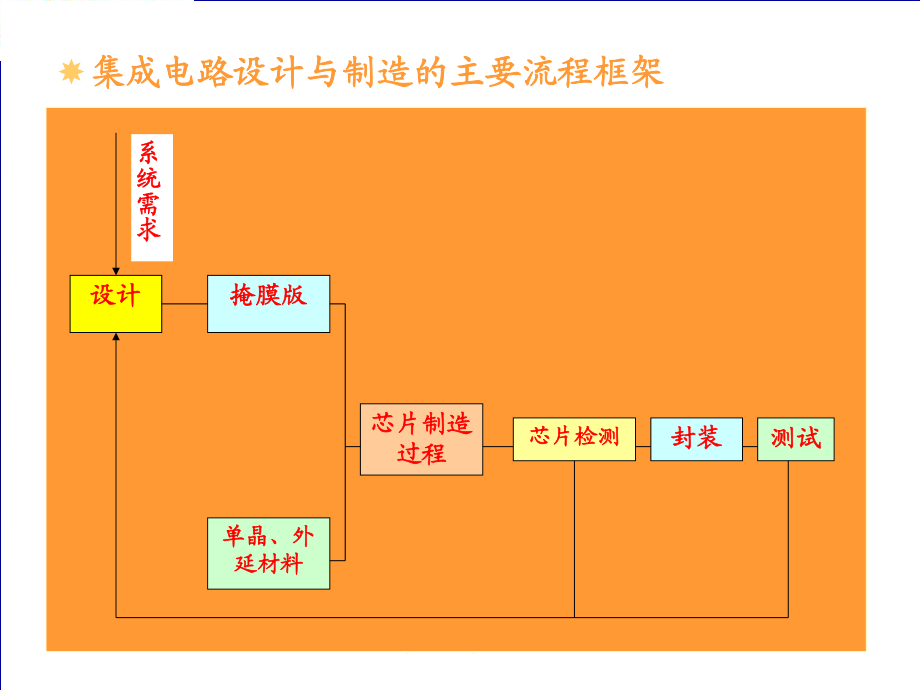

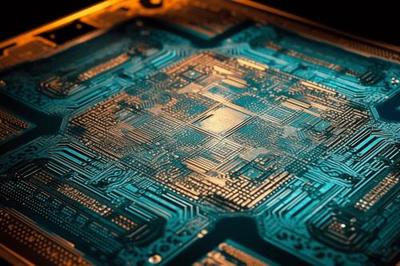

在集成電路設計領域,光刻技術是實現芯片微縮的關鍵環節。隨著摩爾定律的推進,傳統光刻技術面臨分辨率極限的挑戰,促使業界開發出多種先進工藝。本文將對三種主流光刻技術——LELE(光刻-刻蝕-光刻-刻蝕)、SADP(自對準雙重圖案化)和EUV(極紫外光刻)進行全面比較,分析它們的工作原理、優勢、局限以及在集成電路設計中的應用前景。

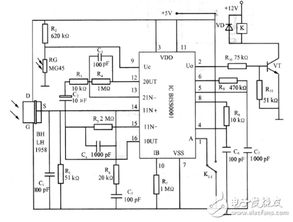

LELE技術是一種雙重圖案化方法,通過兩次獨立的光刻和刻蝕步驟,將單一掩模版的圖案分解為兩個層次,從而提高特征密度。其優點包括工藝相對成熟、成本較低,適用于28納米及以下節點的生產。LELE的多次對齊步驟可能導致疊加誤差,影響良率,且工藝復雜度較高。

SADP技術則利用自對準原理,通過一次光刻和后續的側壁間隔層形成,實現更精細的圖案。SADP在10納米及以下節點中廣泛應用,因其能有效減少疊加誤差,提供更高的分辨率和均勻性。但其工藝步驟復雜,材料成本較高,且對設計規則要求嚴格,可能限制設計靈活性。

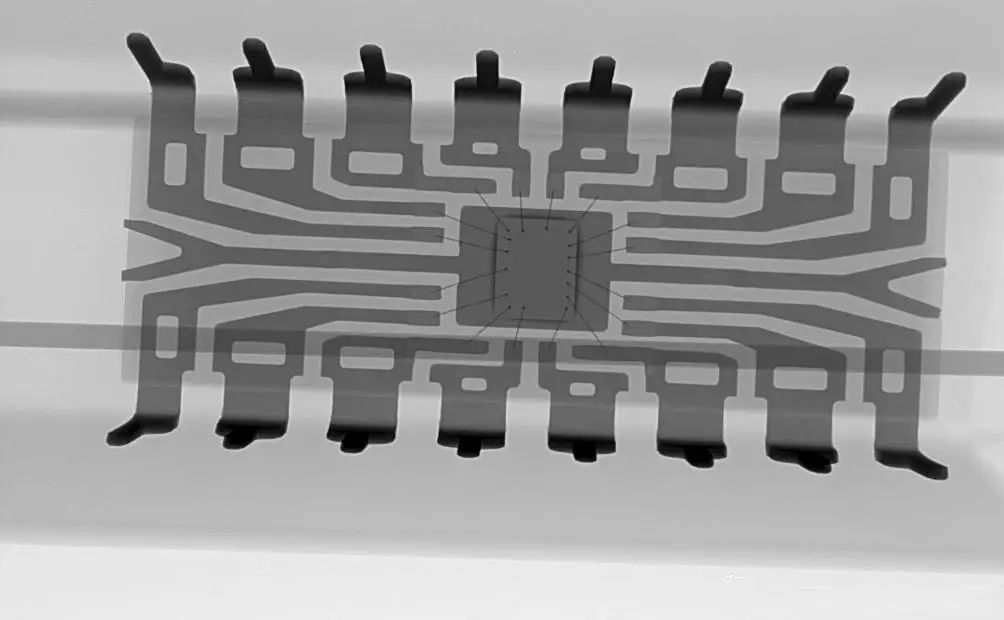

EUV技術作為下一代光刻的突破,采用極紫外光源(波長13.5納米),直接實現高分辨率圖案化,無需多重圖案化步驟。EUV的優勢在于簡化工藝流程、提高生產效率,并支持7納米及以下節點的量產。EUV設備成本高昂、光源功率和掩模缺陷問題仍是挑戰,目前主要應用于高端芯片制造。

在集成電路設計中,選擇合適的光刻技術需綜合考慮性能、成本和設計復雜度。LELE和SADP作為過渡方案,在EUV普及前仍不可或缺;而EUV則代表未來方向,推動芯片向更小尺寸發展。隨著技術演進,這些工藝的融合與優化將持續驅動集成電路創新,滿足高性能計算、人工智能等應用需求。

如若轉載,請注明出處:http://m.hji180.cn/product/22.html

更新時間:2026-03-13 17:29:55