CMOS集成電路設(shè)計中邏輯門電路分析

在CMOS集成電路設(shè)計中,邏輯門電路分析是核心環(huán)節(jié)之一。邏輯門作為構(gòu)建復(fù)雜數(shù)字系統(tǒng)的基本單元,其性能直接關(guān)系到整個集成電路的功耗、速度和可靠性。CMOS技術(shù)因其低功耗和高噪聲容限而成為現(xiàn)代集成電路設(shè)計的主流。以下是邏輯門電路分析的關(guān)鍵方面。

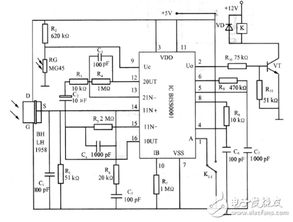

邏輯門的分類包括基本門電路,如反相器(NOT)、與非門(NAND)、或非門(NOR),以及復(fù)合門如異或門(XOR)。在CMOS設(shè)計中,這些門通常采用互補(bǔ)的NMOS和PMOS晶體管對實(shí)現(xiàn),以確保在靜態(tài)狀態(tài)下功耗極低。例如,反相器由一個NMOS和一個PMOS組成,當(dāng)輸入為高電平時,NMOS導(dǎo)通而PMOS截止,輸出低電平;反之亦然。分析時需關(guān)注晶體管的開關(guān)特性和閾值電壓。

邏輯門分析涉及直流特性、交流特性和瞬態(tài)響應(yīng)。直流分析包括計算邏輯門的電壓傳輸特性(VTC),以確定噪聲容限和邏輯電平的穩(wěn)定性。例如,通過繪制VTC曲線,可以評估高、低電平的噪聲容限,確保在工藝波動下電路仍能正常工作。交流分析則關(guān)注頻率響應(yīng),如截止頻率和傳播延遲,這影響電路的處理速度。在高速設(shè)計中,需優(yōu)化晶體管尺寸以減少延遲。

第三,功耗分析是CMOS邏輯門設(shè)計的重點(diǎn)。功耗包括靜態(tài)功耗和動態(tài)功耗。靜態(tài)功耗主要由漏電流引起,在現(xiàn)代工藝下通過使用高K介質(zhì)和多閾值晶體管來抑制。動態(tài)功耗則與開關(guān)活動相關(guān),計算公式為Pdynamic = α * C * Vdd^2 * f,其中α是開關(guān)活動因子,C是負(fù)載電容,V_dd是電源電壓,f是頻率。設(shè)計時需權(quán)衡速度與功耗,例如通過降低電源電壓或優(yōu)化布局來減少電容。

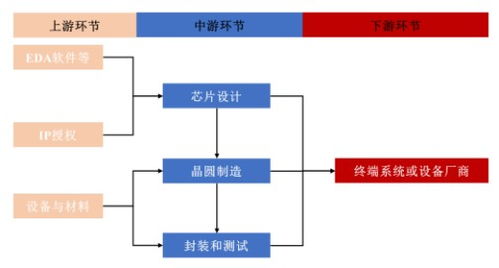

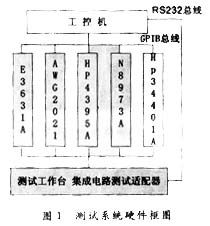

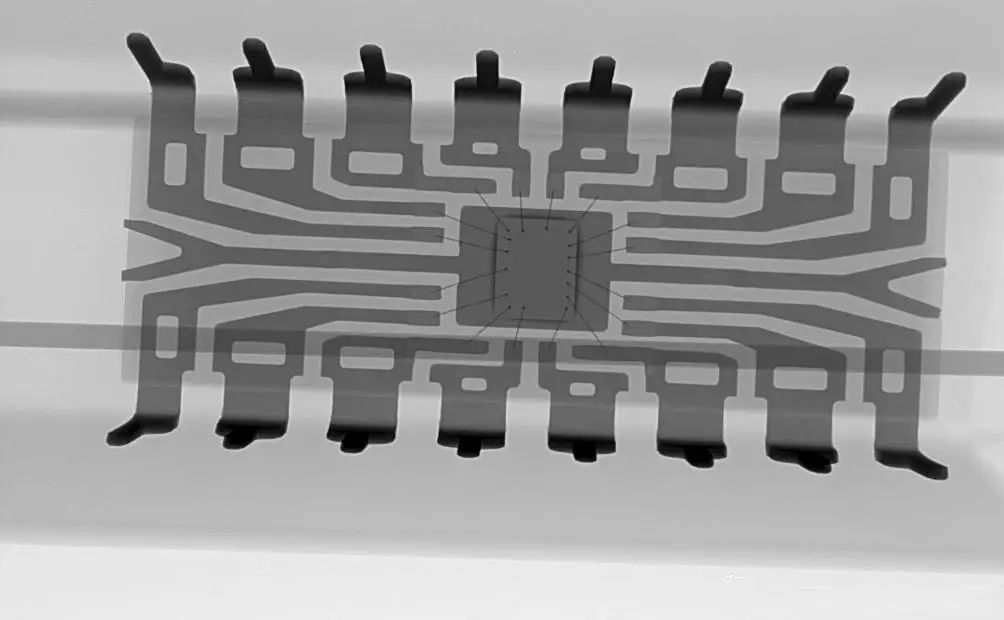

邏輯門的可制造性和可靠性分析也不容忽視。在深亞微米工藝下,需要考慮工藝變異、互連延遲和熱效應(yīng)。通過仿真工具如SPICE,可以模擬不同工藝角下的性能,確保設(shè)計的魯棒性。同時,針對串?dāng)_和電遷移等問題,需進(jìn)行布局優(yōu)化和金屬層規(guī)劃。

CMOS集成電路中的邏輯門電路分析是一個多維度過程,涉及電氣特性、功耗管理和可靠性評估。隨著工藝節(jié)點(diǎn)的不斷縮小,設(shè)計師必須采用先進(jìn)方法,如使用FinFET晶體管和機(jī)器學(xué)習(xí)輔助優(yōu)化,以實(shí)現(xiàn)高性能、低功耗的集成電路。掌握這些分析技能,是成為一名優(yōu)秀集成電路工程師的基礎(chǔ)。

如若轉(zhuǎn)載,請注明出處:http://m.hji180.cn/product/30.html

更新時間:2026-03-13 19:47:33